| Le projet MPC |

|---|

| Problématique |

|---|

Le projet MPC (Multi-PC) du LIP6 (Laboratoire d'Informatique de Paris 6) a démarré en 1995. Il vise à la réalisation d'une machine parallèle de type grappe de PCs à très faible coût. Pour réaliser une machine parallèle de ce type, la problématique est double :

- il faut concevoir des réseaux offrant des débits de l'ordre du Giga-bit par seconde avec des latences de transfert de l'ordre de quelques microsecondes,

- il faut concevoir les couches de communication logicielles permettant aux applications de bénéficier des performances du matériel réseau.

Mon intégration au sein du projet MPC résulte de la deuxième problématique : la réalisation de couches logicielles performantes permettant aux applications d'accéder efficacement au réseau HSL. La recherche de la performance maximale, pour des applications nécessitant une très grande puissance de calcul, ne peut se contenter des progrès importants qu'offre la technologie électronique. L'utilisation parallèle d'un grand nombre de systèmes (de la grappe de PCs à l'ensemble du réseau mondial) devient indispensable. Sur de tels systèmes, le secret pour obtenir de bonnes performances et une programmation aisée est de disposer d'un réseau de communication à faible latence et haut-débit tel que le réseau HSL conçu au LIP6. Quand on met en oeuvre un tel réseau, on se rend très souvent compte a posteriori que les excellentes caractéristiques du matériel sont fortement dégradées par le logiciel. Les logiciels courants se révèlent incapables d'atteindre les performances théoriques du réseau haut-débit sous-jacent. Mes recherches au sein du projet MPC ont pour objectif d'améliorer cette situation autant que faire se peut. Le cadre de mes travaux a été les bibliothèques de communication pour machines parallèles telles que PVM (Parallel Virtual Machine) ou MPI (Message Passing Interface) sur un réseau haut-débit disposant d'une primitive d'écriture en mémoire distante. Je me suis intéressé aux performances de PVM sur la machine MPC dans le cadre de mon stage de DEA. Après avoir constaté une dégradation des performances intrinsèque à PVM et constatant par ailleurs que MPI devenait le standard de fait dans le monde du parallélisme, je me suis attaché pendant ma thèse à la réalisation d'une bibliothèque optimisée du standard MPI pour machines parallèles disposant d'une primitive d'écriture distante.

| Liens |

|---|

- le serveur WEB du projet MPC,

- le matériel du projet MPC,

- le logiciel du projet MPC,

- les membres du projet MPC.

| La machine MPC |

|---|

La machine MPC est une machine parallèle de type grappe de PCs fournissant une primitive d'écriture en mémoire distante.

La philosophie du projet MPC est la même que celle de l'expérimentation NOW de Berkeley : rassembler un ensemble de stations de travail individuelles interconnectées par un réseau rapide et munies d'un ensemble de couches de communications performantes afin d'obtenir une puissance de calcul similaire à celle des supercalculateurs mais à un coût beaucoup plus faible. Sa particularité est d'utiliser un réseau d'interconnexion spécifique conçu au LIP6.

En ce sens, la machine MPC est un cluster dont les composants sont les suivants :

- Les machines individuelles constituant le cluster sont des PCs standard. Chaque noeud de calcul est équipé d'une carte mère standard possédant un chipset et un bus mémoire quelconque, d'une mémoire locale, d'un périphérique de stockage de masse local de quelques Go et d'un bus d'interface PCI 32bits/33Mhz. Un noeud de calcul peut éventuellement être SMP.

- Sur chacun des noeuds de calcul est installé un système d'exploitation Unix standard (FreeBSD ou LINUX).

- Un réseau d'interconnexion rapide entre les différentes machines constituant le cluster : le réseau Gigabit HSL (High Speed Link).

- Un réseau de contrôle bas débit Ethernet 100Mbits/s raccordant l'ensemble des noeuds de calcul ainsi qu'une console.

- Une carte réseau FastHSL par noeud de calcul, sur laquelle se trouvent un routeur (Rcube) et un contrôleur réseau (PCI-DDC) spécifiques au réseau HSL.

- Des couches de communications bas niveau permettant l'accès au réseau HSL.

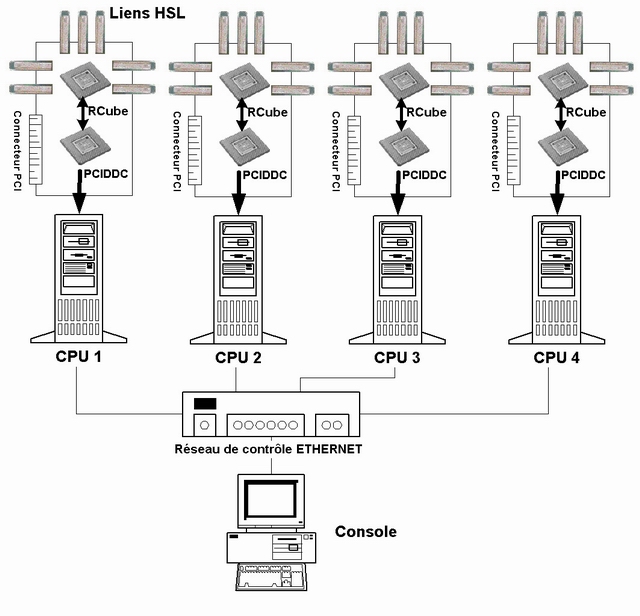

La figure ci-dessous présente la machine MPC du Laboratoire d'Informatique de Paris VI. Elle est constituée de 8 noeuds de calcul possédant chacun deux processeurs PIII-1GHz et 1Go de mémoire (soit 16 processeurs PIII-1GHz et 8 Go de mémoire) ainsi que d'une console servant de serveur de fichiers et permettant aux utilisateurs de lancer leurs applications. Sur la partie droite, on peut distinguer les connecteurs de la carte FastHSL ainsi que les liens HSL.

La machine MPC du LIP6

Architecture d'une machine MPC à quatre noeuds

| Le réseau HSL |

|---|

Le réseau HSL et les couches de communications bas niveau ont été développées par le groupe de recherche MPC.

Le réseau Gigabit de la machine MPC est composé de cartes à interface PCI présentes dans chaque noeud. La carte réseau FastHSL réalise deux fonctions principales : elle contient un processeur câblé qui exécute le protocole de communication, ainsi qu'un routeur intégré qui permet de construire des réseaux de taille et de topologie quelconques. Elle est donc équipée de deux composants VLSI développés au Laboratoire d'Informatique de Paris VI :

- Le routeur rapide Rcube : il s'agit d'un circuit CMOS d'environ 380 000 transistors, qui offre une communication de paquets de type wormhole entre huit ports Gigabit à la norme HSL IEEE-1355. Les paquets du réseau HSL sont constitués d'un en-tête de deux octets qui spécifie entre autres la destination des paquets. Un paquet peut avoir une taille quelconque.

- Le contrôleur réseau PCI-DDC : un circuit CMOS d'environ 200 000 transistors qui implémente une primitive d'écriture distante en mémoire à travers le réseau HSL. Il assure l'interface entre le bus PCI et le routeur Rcube. Il accède directement à la mémoire du noeud local par accès DMA (Direct Memory Access) en lecture comme en écriture, ce qui décharge le processeur local pendant les transferts de données.

La figure ci-dessous représente la carte FastHSL. On peut distinguer sur la photographie les deux composants VLSI développés par le groupe de recherche MPC. A droite se trouve le composant PCIDDC et à gauche Rcube.

La carte FastHSL

Last modified: